Fundamentals of Computer Engineering

ELEC 220

Combine CS and EE to design and implement an optimized computing system.

- the processor gets instructions and data from the memory

- input writes data to the memory

- output reads data from the memory

- control sends the signal that determind the operations of the…

- datapath, which does computations

History §

Babbage §

- diff engine

- George Scheutz

- analytical engine

- Scheutz

Binary §

Unsigned binary integers §

Range: to

2’s complement signed integers §

MSB is the sign bit.

Range: to

- Most positive:

- Most negative:

Overflow §

Sum requires more bits than the input data width.

| No | Maybe | |

| Maybe | No |

| Maybe | No | |

| No | Maybe |

Sign extension §

move 2’s complement signed int from smaller to larger container: replicate the sign bit to the left

Floating Points §

- normalized

- not normalized

IEEE 754-1985 standard.

Types:

- single precision — 32 bits

- double precision — 64 bits

Components:

-

sign (1 bit)

-

exponent (8 vs 11 bits)

implicit bias 😏 (127 vs 1023)

-

fraction (23 vs 52 bits)

special cases

-

-

subnormal/denormal numbers.

-

literally

-

-

-

NaN aka Not a Number.

-

-

Memory §

Byte ordering §

- Big Endian — LSB has highest address

- Little Endian — LSB has lowest address

Example (0x07AB9DCE):

| Address | B.E. value | L.E. value |

|---|---|---|

| … | … | … |

0x70 |

07 |

CE |

0x71 |

AB |

9D |

0x72 |

9D |

AB |

0x73 |

CE |

07 |

| … | … | … |

Addresses, data.

-

: Kibibyte (KiB)

-

: Mebibyte (Mib)

-

…

-

Microprocessor

CPU components. No memory, no I/O.

-

Microcomputer

Has memory, some I/O.

-

Microcontroller

Many types of memory, sophisticated I/O.

TM4C123GH6PM §

Memory:

- Flash 256 KiB

- SRAM 32 KiB

- ROM

C §

Pointers §

components:

- value: address location

- type: the type of the data at the stored address

- read operands only from the register file

- write operations only to the register file

- only one way to move data between the register file and data memory

- data addresses

- instruction addresses

Bitwise operators §

-

~a— not -

a & b— andx & 0 = 0;x & 1 = x. clear -

a | b— orx | 0 = x;x | 1 = 1. set -

a ^ b— xorx ^ 0 = x;x ^ 1 = ~x -

a >> n— right shift -

a << n— left shift

RISC V §

Reduced Instruction Set Computing.

RISC-V has 32 registers. x0 through x31. Have no type.

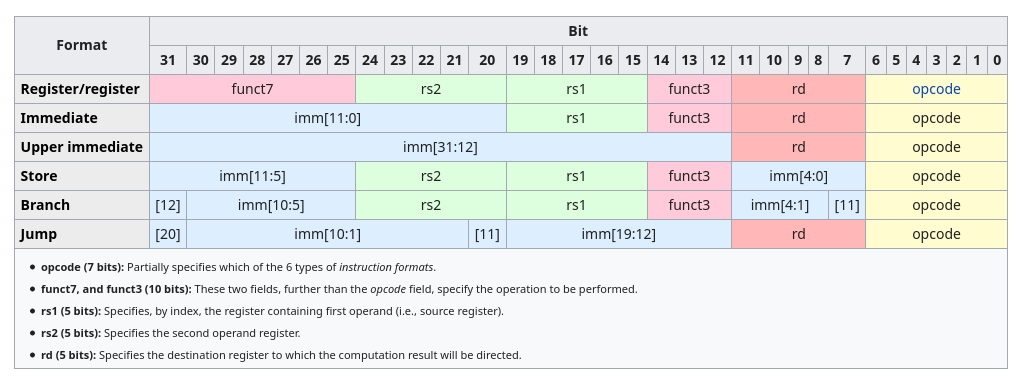

R-format — register-register arithmetic §

| Operation | OP Code | funct7 | funct3 |

|---|---|---|---|

ADD |

0110011 |

0000000 |

000 |

SUB |

0110011 |

0100000 |

000 |

SLL |

0110011 |

0000000 |

001 |

SLT |

0110011 |

0000000 |

010 |

SLTU |

0110011 |

0000000 |

011 |

XOR |

0110011 |

0000000 |

100 |

SRL |

0110011 |

0000000 |

101 |

SRA |

0110011 |

0100000 |

101 |

OR |

0110011 |

0000000 |

110 |

AND |

0110011 |

0000000 |

111 |

I-format — register-immediate arithmetic §

S-format — stores §

B-format — branches §

U-format — 20-bit upper immediate §

J-format — jumps §

Instructions §

-

add -

lw— load wordlw dest,offset(source) -

sw— store wordsw dest,offset(source) -

lb— load bytelb dest,offset(source) -

sb— store bytesb dest,offset(source) -

slli— shift left (logical)slli dest,source,bits -

srai— shift right (arithmetic) -

beq— branch (if) equal -

bne— branch (if) not equal -

blt— branch (if) less than -

bge— branch (if) less than -

j— jump

Analog to Digital §

input: continous time signal

output: discrete sequence

Logic Design §

Demultiplexer

Multiplexer

Canonical forms:

- POS

- SOP

Transistors:

- n

- p

Cache §

memory hierarchy.

trade-off between speed and price/size. small, fast vs large, slow.

locality:

- temporal locality

- spatial locality

types:

- direct-mapped cache

- set associative cache

data bytes

- . when direct-mapped,

Word length: